# **Transparent and Flexible Graphene Charge-Trap Memory**

Sung Min Kim,<sup>†,#</sup> Emil B. Song,<sup>†,#</sup> Sejoon Lee,<sup>†,‡,\*</sup> Jinfeng Zhu,<sup>†</sup> David H. Seo,<sup>§</sup> Matthew Mecklenburg,<sup>⊥</sup> Sunae Seo,<sup>¶</sup> and Kang L. Wang<sup>†</sup>

<sup>†</sup>Electrical Engineering Department, University of California, Los Angeles, California 90095, United States , <sup>‡</sup>Quantum-Functional Semiconductor Research Center, Dongguk University-Seoul, Seoul 100-715, Korea, <sup>§</sup>Samsung Advanced Institute of Technology, Yongin, 446-711, Korea, <sup>⊥</sup>Microelectronics Technology Department, The Aerospace Corporation, Los Angeles, California 90009, United States , and <sup>¶</sup>Department of Physics, Sejong University, Seoul 143-747, Korea. <sup>#</sup>These authors contributed equally to this work.

lectronic modules have been going through extensive renovations in order to incorporate multiple functionalities, such as portability, transparency, flexibility, and wearability. This would require multiple core electronic devices, such as logic, memory, and display to be integrated on a single transparent-flexible substrate without degrading the transparency from the addition of active layers and device performance under flex. In the past decade, difficulties in achieving transparent high-quality crystalline inorganic materials on transparent-flexible substrates have made organic materials<sup>1,2</sup> and semiconducting nanowires<sup>3,4</sup>/nanotubes<sup>5,6</sup> favorable for transparent-flexible electronic devices.<sup>7,8</sup>

Alternatively, the two-dimensional graphene can offer enhanced performance to transparent-flexible electronic modules because it inherently possesses high carrier mobility<sup>9</sup> with minimal light absorbance.<sup>10</sup> Furthermore, due to the strong hexagonal covalent bonds, graphene maintains its extraordinary mechanical properties even at the nanoscale regime.<sup>11</sup> In recent years, the success of artificially growing large scale graphene<sup>12,13</sup> has led to graphene-based transparent electrodes,<sup>10</sup> which transcended to the emergence of graphene-based touch screen, liquid crystal display, organic solar cells, and organic light emitting diodes. In addition to graphene being exploited as a passive element, flexible and stretchable graphene transistors have also been demonstrated using an ion-gel gate dielectric.<sup>14,15</sup>

The single atomic profile and the astonishing physical properties of graphene can also allow advancements in a variety of memory metrics when implemented into several types of memory architectures. For example, in recent years, various types of graphene-based memory devices have been demonstrated; for example, a flash memory with graphene floating-gate,<sup>16</sup> ferroelectric memories with

#### ABSTRACT

A transparent and flexible graphene charge-trap memory (GCTM) composed of a single-layer graphene channel and a 3-dimensional gate stack was fabricated on a polyethylene naphtalate substrate below eutectic temperatures ( $\sim$ 110 °C). The GCTM exhibits memory functionality of  $\sim$ 8.6 V memory window and 30% data retention per 10 years, while maintaining  $\sim$ 80% of transparency in the visible wavelength. Under both tensile and compressive stress, the GCTM shows minimal effect on the program/erase states and the on-state current. This can be utilized for transparent and flexible electronics that require integration of logic, memory, and display on a single substrate with high transparency and endurance under flex.

**KEYWORDS:** graphene · nonvolatile memory · charge-trap memory · transparent · flexible

graphene channel,<sup>17,18</sup> charge-trap memories using dielectric stacks on graphene channel,<sup>19,20</sup> resistive memories using reduced graphene-oxide,<sup>21,22</sup> and nanoelectromechanical switches using graphene beams.<sup>23,24</sup> In addition, by integrating graphene with polymers and/or flexible substrates,<sup>25–28</sup> a spectrum of graphene-based memory applications is streaming toward transparent flexible- and wearableelectronics. Transparent-flexible memory modules, however, have been limited to memristive systems.

In this paper, we show memory operation in transparent-flexible graphene chargetrap memory (GCTM) devices that are fabricated on a transparent-flexible polyethylene naphthalate (PEN) substrate. The GCTM is composed of a single-layer graphene channel field-effect transistor with a triple high-*k* dielectric ( $Al_2O_3$ /HfO<sub>x</sub>/ $Al_2O_3$ ) gate-oxide stack. \* Address correspondence to sejoon@ee.ucla.edu, sejoon@dongguk.edu.

Received for review May 18, 2012 and accepted August 13, 2012.

**Published online August 13, 2012** 10.1021/nn302193q

© 2012 American Chemical Society

VOL.6 • NO.9 • 7879-7884 • 2012

7879

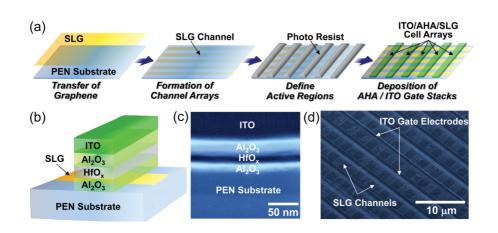

Figure 1. (a) Fabrication process steps of transparent-flexible GCTM. (b) Schematic illustration of GCTM device structure. (c) Crosssectional TEM image of Al<sub>2</sub>O<sub>3</sub>/HfO<sub>x</sub>/Al<sub>2</sub>O<sub>3</sub> (AHA) gate stack in GCTM. (d) Bird's eye view SEM image of high-density GCTM array.

Although the memory performance can be characterized through many means, we focus on the degradation of transparency due to the active graphene/triplegate stack, the operating mechanism, and retention properties of the memory function, and the influence of bending stress on the device performance.

## **RESULTS AND DISCUSSION**

Most transparent-flexible substrates cannot withstand high temperatures associated with processing steps necessary for device fabrication due to the low glass transition and/or thermal decomposition temperatures of the substrate. An advantage in using graphene as an active layer is to eliminate high temperature processes that are generally required for obtaining high quality channel materials and Ohmic source/drain junctions. Here, we fabricate the transparent-flexible GCTM through a multistep procedure at temperatures below 110 °C as shown in Figure 1a. First, single-layer graphene was grown on a copper film by plasma-enhanced chemical vapor deposition (CVD),<sup>16,29</sup> transferred onto a PEN substrate, and characterized through Raman spectroscopy (see Supporting Information).<sup>16,17,20,29,30</sup> Active channel regions were then patterned by photolithography and etched through oxygen plasma. Next, a photoresist mask was formed by photolithography and a thin Al layer of 12 Å was deposited and oxidized in air to promote nucleation of Al<sub>2</sub>O<sub>3</sub>.<sup>16,31</sup> Finally, a triple-gate stack of Al<sub>2</sub>O<sub>3</sub>/HfO<sub>4</sub>/Al<sub>2</sub>O<sub>3</sub> (8 nm/8 nm/ 25 nm) was subsequently deposited through atomic layer deposition, and transparent indium tin oxide (ITO) gate electrodes were formed by sputtering and lift-off. The schematic diagram, cross-sectional transmission electron microscope (TEM) image of the as fabricated GCTM, and scanning electron microscope (SEM) image of the highdensity GCTM array are shown in Figure 1b-d. The triple gate stack comprising an Al<sub>2</sub>O<sub>3</sub> tunnel oxide, a HfO<sub>x</sub> charge trap layer, and an Al<sub>2</sub>O<sub>3</sub> control oxide is clearly noticeable. The SEM image of the array (Figure 1d) is to demonstrate a possible cell circuitry composed of GCTMs without metal electrodes. The semimetallic property of graphene allows the graphene to be used as either the channel material or

the interconnections. In other words, the region of graphene underneath the gate stack serves as the channel material, while the rest of graphene may function as both the source/drain contacts and interconnections.

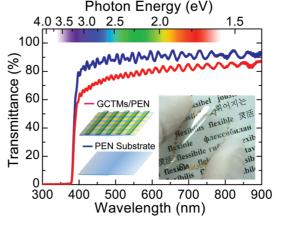

We first examine the transparency degradation arising from the addition of GCTM on the PEN substrate. Figure 2 compares the optical transmittance spectra of the PEN substrate with and without the GCTM array. The active layers reduce the transparency only by 8% in the visible-infrared wavelength range (400-900 nm) and sustain its transparency without distorting an image behind the GCTM array (inset of Figure 2). Minimum requirement for transparency for an active electronic element should be greater than 80% considering the transparency of a transparent electrode is nowadays above 90%.<sup>32</sup> Up to date, transparency ranging in 60-80% has been demonstrated in various transparent electronic modules; for example, semiconducting nanowires/nanotube transistors and logic gates (>80%),<sup>4,5,33,34</sup> wide bandgap transparent conducting oxide memory structures ( $\sim$ 80%),<sup>35</sup> organic light emitting diodes (~70%),<sup>36</sup> and grid structured lithium-ion batteries (~60%).<sup>37</sup> Our GCTM array shows transmittance over

KIM ET AL.

VOL.6 • NO.9 • 7879-7884 • 2012

IAI

www.acsnano.org

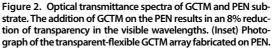

Figure 3. Operation mechanism of GCTM. (a) Band diagram of GCTM across the gate stack. The program and erase operation are based on electron and hole injection, which depends on the polarity of the gate voltage. (b) Typical memory functions of GCTM in air at  $V_{\rm D} = 1$  V. The device shows a shift of Dirac point under gate voltage stress.

80% in the visible-infrared regions, which is comparable to the most transparent active components.

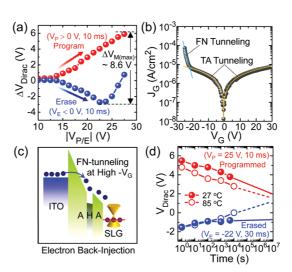

Next, we study the electrical performance of the GCTM where all electrical measurements were taken on individual GCTM devices with channel dimensions (W/L  $\approx$  4.5  $\mu$ m/30  $\mu$ m) and Ti/Al (10 nm/100 nm) source/drain contacts due to the difficulties in probing the monolayer graphene electrodes. The operational mechanism of the program/erase mode in our GCTM is illustrated in Figure 3a, where the energy band diagrams were represented on the basis of the Anderson model<sup>38</sup> (see Supporting Information). In the program (erase) mode, where the gate is under a positive (negative) voltage, the internal electric-field within the gate stack and the thin Al<sub>2</sub>O<sub>3</sub> tunneling oxide permits electrons (holes) from the graphene to be injected into the  $HfO_x$  charge trap layer. The trapped electrons (holes) effectively dope the graphene to p-type (n-type) and results in a positive (negative) shift of  $V_{\text{Dirac}}$ . This is shown in Figure 3b, where a positive (negative) shift of V<sub>Dirac</sub> occurs upon applying a program (erase) voltage pulse of  $V_{\rm P} = 23$  V ( $V_{\rm E} = -21$  V). The trapped charges in the charge trap layer modify the energy band alignment of the gate stack and lead to a memory effect in the device characteristics. The change of the electrochemical potential within the gate stack leads to the shift of the Dirac point ( $\Delta V_{\text{Dirac}}$ ), from which the memory window ( $\Delta V_{\rm M}$ ) of the GCTM can be defined.

The memory window of charge-trap memories is determined by the number of trapped charges in the charge storage layer, which rely on the magnitude of program/erase voltages. Thus, we examine the  $\Delta V_{\text{Dirac}}$ at various magnitudes of  $|V_{P/E}|$ . As shown in Figure 4a,

Figure 4. Electrical characteristics in air of GCTM. (a) Memory window as a function of program/erase voltage. A maximum window of  $\sim$ 8.6 V is achieved. Electron back injection starts to occur at erase voltage of cq. -22 V. (b) Gate tunneling current density. The tunneling mechanism for the standard program/erase operation corresponds to trap-assisted (TA) tunneling and the electron-back injection arises through Fowler-Nordheim (FN) tunneling. (c) Illustration of the electron back-injection mechanism associated with Fowler-Nordheim tunneling. (d) Retention characteristics of GCTM. For all of the measurements, V<sub>D</sub> was fixed at 1 V.

the memory effect starts at a voltage pulse of  $|V_{\rm P/E}| pprox$ 14 V and increases monotonically as  $|V_{P/E}|$  increases, resulting in a maximum memory window of  $\Delta V_{M(max)}$ pprox 8.6 V. However, the  $\Delta V_{\text{Dirac}}$  suddenly reduces after  $V_{\rm E} pprox -24$  V. This is attributed to the electron backinjection from the ITO gate to the charge trap layer via Fowler-Nordheim tunneling (Figure 4c). When a negative erase voltage is applied, the charge trap layer is filled with holes and the back injected electrons compensate the overall positively stored charges, resulting in a reduction of  $\Delta V_{\text{Dirac}}$ . To further investigate the transport mechanism of the device, we measure the gate tunneling current of the GCTM. As shown in Figure 4b, the parabolic dependence shows trapassisted (TA) tunneling<sup>39</sup> as the normal write/erase mechanism, whereas the linear relation below  $V_{\rm E} \approx -24$  V indicates Fowler-Nordheim (FN) tunneling<sup>39,40</sup> to be responsible for the electron back-injection. To suppress or eliminate such effects, a high work-function gate material would be favorable because it will modify the flat band condition and increase the tunneling barrier of the control oxide layer making it difficult for the back-injection to occur.<sup>20</sup> In addition to the large memory window, the GCTM shows 30% data retention per 10 years at room temperature (Figure 4d). At elevated temperatures, the retention characteristics degrade. We noticed that the PEN substrate thermally expands at 85 °C. One possibility of such meager retention is the quality of the tunnel oxide formed at low temperatures. Since the glass transition temperature of the PEN substrate is  $\sim$ 200 °C, we carried out all of the fabrication steps below 110 °C. This might cause the formation of point defects in

JAI

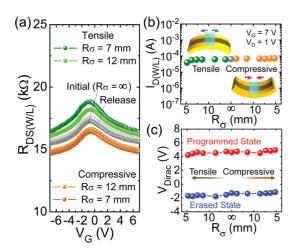

Figure 5. Endurance of electrical characteristics in air under flex. (a) Normalized resistance vs gate voltage under tensile and compressive stress at  $V_D = 1$  V. The GCTM reveals minimal Dirac point shift and channel transconductance change under bending. (b) On-state current under bending stress measured at  $V_D = 1$  V and  $V_G = 7$  V. (c) Position of Dirac point under bending stress at program/erase states ( $V_P = 23$ V,  $V_E = -21$  V). For flexures below 7 mm bending curvature, the device remains unchanged after more than 10 cycles.

the tunnel oxide layer and diminish the retention characteristics. Thus, optimizing the process to achieve high quality tunnel oxides at low temperature would be vital to improve the retention characteristics.

Flexible electronics require its functions to sustain under geometric deformation. They will need to be rolled or folded to maximize portability and wearability. The extremely large intrinsic breaking strength of 130 GPa makes graphene resilient to fracture upon stress.<sup>41</sup> On the other hand, the high Young's modulus of graphene (~1 TPa) is sought to be undesirable for deformation, but the atomic thinness makes graphene an exception.<sup>42,43</sup> In some sense, the flexibility of graphene stems from similar reasons to why graphene exhibits a negative thermal expansion coefficient.<sup>44–46</sup> Figure 5a displays the response of normalized resistance  $(R_{DS(W/L)} - V_G)$  under flex. Since the channel dimension (i.e., overlap region between gate oxide and graphene) is  $W/L \approx 4.5 \ \mu m/30 \ \mu m$ , the stress effect would be pronounced along the L direction. Thus, we performed the effect of bending stress along the channel direction. The asymmetric device structure along its vertical direction makes it worthwhile to investigate the impact of both tensile and compressive stress ( $R_{ci}$ ; bending radius). The GCTM shows no change in the position of the Dirac point, which suggests the potential profile of the energy bands along the gate electrode and dielectric are stable under bending. Furthermore, no significant change in the slope at the linear regime indicates that the graphene channel is robust under stress. From the channel transconductance ( $g_m \propto \mu$ ), the average electron/hole mobility ( $\mu$ ) of multiple devices is estimated to be ~67 cm<sup>2</sup>/(V·s) and varied up to 10% under flex. The slight change in resistance might be due to the contact regions, which requires further investigation.<sup>47</sup> As a consequence, as shown in Figure 5b and 5c, the on-state current measured at  $V_D = 1$  V and  $V_G = 7$  V remains steady, while the Dirac point at the program ( $V_P = 23$  V) and erase ( $V_E = -21$  V) states stays unaffected. Here, we note that ITO is not a highly flexible material; that is, ITO can sustain up to 2.5% of strain without affecting its conductance.<sup>48</sup> Thus, replacing ITO with graphene or transparent-conducting organic materials (*e.g.*, PEDOT:PSS) as the gate electrode would be beneficial to further improve the flexibility of GCTM.

The ON/OFF ratio of graphene-based devices is still an ongoing challenge in the graphene community. Several methods have been proposed to create an energy bandgap in this otherwise gapless material. For example, graphene nanoribbons show that a bandgap of  $\leq$  50 meV can be achieved through quantum confinement effects,<sup>49</sup> and bi or trilayer graphene exhibits a bandgap of  $\leq$  250 meV under high electric fields.<sup>50,51</sup> In addition, very recently, the usage of Schottky source/ drain contacts have shown to improve the ON/OFF ratio of graphene transistors.<sup>30</sup> Implementing such behaviors in our device structure should be the next step to improve the memory performance of graphene-based charge trap flash memory structures.

The operating speed of our graphene charge trap memory would be limited by the capacitive charging speed of the gate stack, since the high graphene mobility<sup>52,53</sup> of 5000 to 100 000 cm<sup>2</sup>/(V s) renders an extremely short transit time. Therefore, the GCTM structure will have similar operating speeds as the standard charge trap memories, which currently show ~14 ns read time and 20  $\mu$ s/20 ms write/erase time.<sup>54</sup>

## CONCLUSION

The covalently bonded graphene greatly reduces the heat budget and enables fabrication of ultrahigh density transparent-flexible GCTM. The GCTM only reduces 8% of transparency from the PEN substrate and demonstrates memory functionality of 8.6 V memory window with reasonable retention characteristics. Furthermore, the electrical characteristics of the transparent-flexible GCTM exhibit minimal perturbation due to the bending stress. We believe that graphenebased electronic modules will help bring future electronics a step closer to transparent-flexible electronics.

#### MATERIALS AND METHODS

Graphene Growth and Transfer. The CVD graphene was prepared by depositing a Cu thin film of 500 nm thickness, using electron-beam evaporation, on a SiO<sub>2</sub>/Si wafer and placed in an inductively coupled plasma enhanced CVD (PECVD) chamber. The substrate temperature was increased to 650 °C at a base

VOL.6 • NO.9 • 7879-7884 • 2012 A

pressure of  $5 \times 10^{-7}$  Torr and hydrogen plasma was applied for a surface treatment at 650 °C. The monolayer graphene was then grown under an Ar + C<sub>2</sub>H<sub>2</sub> gas plasma mixture at 50 mTorr for 3 min. The as-grown graphene film was then transferred to the PET film after removal from the Cu/SiO<sub>2</sub>/Si wafer. A spincoated polymethylmethacrylate (PMMA) and adhesive ultraviolet-tape was placed over the graphene as a protective layer. After peeling the Cu/graphene/PMMA/tape from the growth substrate, the Cu thin film was removed in a dilute FeCl<sub>3</sub> solution and the remains were transferred onto the PET substrate. Then, the PMMA and tape were removed by organic solvents.

**Electrical and Transmittance Measurements.** The electrical characteristics were measured through a semiconductor analyzer (Keithley 4200) under ambient conditions, and the radius of curvature was measured by a stylus profiler. The optical transmittance was taken by a UV-vis-NIR spectrometer (Ocean Optics 2000).

Conflict of Interest: The authors declare no competing financial interest.

Acknowledgment. This work was supported by the Focus Center Research Program (FCRP)—Functional Engineered Nano Architectonics (FENA) and the NSF IGERT Materials Creation Training Program Grant DGE-11443. The work at The Aerospace Corporation was supported under its Independent Research and Development program.

Supporting Information Available: This section includes the Raman characteristics of SLG and the quantitative representation of the energy band diagram for GCTM. This material is available free of charge via the Internet at http://pubs.acs.org.

### **REFERENCES AND NOTES**

- Cho, B.; Song, S.; Ji, Y.; Kim, T.-W.; Lee, T. Organic Resistive Memory Devices: Performance Enhancement, Integration, and Advanced Architectures. *Adv. Funct. Mater.* 2011, *21*, 2806–2829.

- Forrest, S. R. The Path to Ubiquitous and Low-Cost Organic Electronic Appliances on Plastic. *Nature* 2004, 428, 911–918.

- Kim, D.-H.; Ahn, J.-H.; Choi, W. M.; Kim, H.-S.; Kim, T.-H.; Song, J.; Huang, Y. Y.; Liu, Z.; Lu, C.; Rogers, J. A. Stretchable and Foldable Silicon Integrated Circuits. *Science* 2008, 320, 507–511.

- Ju, S.; Facchetti, A.; Xuan, Y.; Liu, J.; Ishikawa, F.; Ye, P.; Zhou, C.; Marks, T. J.; Janes, D. B. Fabrication of Fully Transparent Nanowire Transistors for Transparent and Flexible Electronics. *Nat. Nanotechnol.* **2007**, *2*, 378–384.

- Yu, W. J.; Lee, S. Y.; Chae, S. H.; Perello, D.; Han, G. H.; Yun, M.; Lee, Y. H. Small Hysteresis Nanocarbon-Based Integrated Circuits on Flexible and Transparent Plastic Substrate. *Nano Lett.* 2011, *11*, 1344–1350.

- Cao, Q.; Kim, H.-S.; Pimparkar, N.; Kulkarni, J. P.; Wang, C.; Shim, M.; Roy, K.; Alam, M. A.; Rogers, J. A. Medium-Scale Carbon Nanotube Thin-Film Integrated Circuits on Flexible Plastic Substrates. *Nature* **2008**, *454*, 495–500.

- 7. Wager, J. F.; Keszler, D. A.; Presley, R. E. *Transparent Electronics*; Springer Science: New York, 2010.

- 8. Wong, W. S.; Salleo, A. *Flexible Electronics: Materials and Applications*; Springer Science: New York, 2009.

- Schwierz, F. Graphene Transistors. Nat. Nanotechnol. 2010, 5, 487–496.

- Pang, S.; Hernandez, Y.; Feng, X.; Müllen, K. Graphene as Transparent Electrode Material for Organic Electronics. *Adv. Mater.* 2011, 23, 2779–2795.

- Barton, R. A.; Parpia, J.; Craighead, H. G. Fabrication and Performance of Graphene Nanoelectromechanical Systems. J. Vac. Sci. Technol., B 2011, 29, 050801.

- Li, X.; Cai, W.; An, J.; Kim, S.; Nah, J.; Yang, D.; Piner, R.; Velamakanni, A.; Jung, I.; Tutuc, E.; Retagging of a Long Base Character in an msub, msup, or msubsup Large-Area Synthesis of High-Quality and Uniform Graphene Films on Copper Foils. *Science* **2009**, *324*, 1312–1314.

- 13. Kim, K. S.; Zhao, Y.; Jang, H.; Lee, S. Y.; Kim, J. M.; Kim, K. S.; Ahn, J.-H.; Kim, P.; Choi, J.-Y.; Hong, B. H. Large-Scale

- Kim, B. J.; Jang, H.; Lee, S.-K.; Hong, B. H.; Ahn, J.-H.; Cho, J. H. High-Performance Flexible Graphene Field Effect Transistors with Ion Gel Gate Dielectrics. *Nano Lett.* **2010**, *10*, 3464–3466.

- Lee, S.-K.; Kim, B. J.; Jang, H.; Yoon, S. C.; Lee, C.; Hong, B. H.; Rogers, J. A.; Cho, J. H.; Ahn, J.-H. Stretchable Graphene Transistors with Printed Dielectrics and Gate Electrodes. *Nano Lett.* **2011**, *11*, 4642–4646.

- Hong, A. J.; Song, E. B.; Yu, H. S.; Allen, M. J.; Kim, J.; Fowler, J. D.; Wassei, J. K.; Park, Y.; Wang, Y.; Zou, J.; *et al.* Graphene Flash Memory. *ACS Nano* **2011**, *5*, 7812–7817.

- Song, E. B.; Lian, B.; Kim, S. M.; Lee, S.; Chung, T.-K.; Wang, M.; Zeng, C.; Xu, G.; Wong, K.; Zhou, Y.; *et al.* Robust Bistable Memory Operation in Single-Layer Graphene Ferroelectric Memory. *Appl. Phys. Lett.* **2011**, *99*, 042109.

- Zheng, Y.; Ni, G.-X.; Toh, C.-T.; Tan, C.-Y.; Yao, K.; Özyilmaz, B. Graphene Field-Effect Transistors with Ferroelectric Gating. *Phys. Rev. Lett.* **2010**, *105*, 166602.

- Imam, S. A.; Deshpande, T.; Guermoune, A.; Siaj, M.; Szkopek, T. Charge Transfer Hysteresis in Graphene Dual-Dielectric Memory Cell Structures. *Appl. Phys. Lett.* **2011**, *99*, 082109.

- Lee, S.; Song, E. B.; Kim, S.; Seo, D. H.; Seo, S.; Kang, T. W.; Wang, K. L. Impact of Gate Work-Function on Memory Characteristics in Al<sub>2</sub>O<sub>3</sub>/HfO<sub>x</sub>/Al<sub>2</sub>O<sub>3</sub>/Graphene Charge-Trap Memory Devices. *Appl. Phys. Lett.* **2012**, *100*, 023109.

- He, C. L.; Zhuge, F.; Zhou, X. F.; Li, M.; Zhou, G. C.; Liu, Y. W.; Wang, J. Z.; Chen, B.; Su, W. J.; Liu, Z. P.; *et al.* Nonvolatile Resistive Switching in Graphene Oxide Thin Films. *Appl. Phys. Lett.* **2009**, *95*, 232101.

- Wang, S.; Pu, J.; Chan, D. S. H.; Cho, B. J.; Loh, K. P. Wide Memory Window in Graphene Oxide Charge Storage Nodes. *Appl. Phys. Lett.* **2010**, *96*, 143109.

- Milaninia, K. M.; Baldo, M. A.; Reina, A.; Kong, J. All Graphene Electromechanical Switch Fabricated by Chemical Vapor Deposition. *Appl. Phys. Lett.* 2009, *95*, 183105.

- Kim, S. M.; Song, E. B.; Lee, S.; Seo, S.; Seo, D. H.; Hwang, Y.; Candler, R.; Wang, K. L. Suspended Few-layer Graphene Beam Electromechanical Switch with Abrupt on-off Characteristics and Minimal Leakage Current. *Appl. Phys. Lett.* 2011, 99, 023103.

- Hong, S. K.; Kim, J. E.; Kim, S. O.; Choi, S.-Y.; Cho, B. J. Flexible Resistive Switching Memory Device Based on Graphene Oxide. *IEEE Electron Dev. Lett.* **2010**, *31*, 1005–1007.

- Jeong, H. Y.; Kim, J. Y.; Kim, J. W.; Hwang, J. O.; Kim, J.-E.; Lee, J. Y.; Yoon, T. H.; Cho, B. J.; Kim, S. O.; Ruoff, R. S.; et al. Graphene Oxide Thin Films for Flexible Nonvolatile Memory Applications. *Nano Lett.* **2010**, *10*, 4381–4386.

- Son, D. I.; Kim, T. W.; Shim, J. H.; Jung, J. H.; Lee, D. U.; Lee, J. M.; Park, W. I.; Choi, W. K. Flexible Organic Bistable Devices Based on Graphene Embedded in an Insulating Poly(methyl methacrylate) Polymer Layer. *Nano Lett.* 2010, *10*, 2441–2447.

- Ji, Y.; Lee, S.; Cho, B.; Song, S.; Lee, T. Flexible Organic Memory Devices with Multilayer Graphene Electrodes. ACS Nano 2011, 5, 5995–6000.

- Jeon, I.; Yang, H.; Lee, S.-H.; Heo, J.; Seo, D. H.; Shin, J.; Chung, U. I.; Kim, Z. G.; Chung, H.-J.; Seo, S. Passivation of Metal Surface States: Microscopic Origin for Uniform Monolayer Graphene by Low Temperature Chemical Vapor Deposition. ACS Nano 2011, 5, 1915–1920.

- Yang, H.; Heo, J.; Park, S.; Song, H. J.; Seo, D. H.; Byun, K.-E.; Kim, P.; Yoo, I.; Chung, H.-J.; Kim, K. Graphene Barristor, a Triode Device with a Gate-Controlled Schottky Barrier. *Science* 2012, 336, 1140–1143.

- Kim, S.; Nah, J.; Jo, I.; Shahrjerdi, D.; Colombo, L.; Yao, Z.; Tutuc, E.; Banerjee, S. K. Realization of a High Mobility Dual-Gated Graphene Field-Effect Transistor with Al<sub>2</sub>O<sub>3</sub> Dielectric. *Appl. Phys. Lett.* **2009**, *94*, 062107.

- Ellmer, K.; Klein, A.; Rech, B. Transparent Conductive Zinc Oxide: Basics and Applications in Thin Film Solar Cells; Springer: Berlin, Heidelberg, 2010.

- Lee, D.; Yi, J.; Lee, W.; Paik, U.; Rogers, J.; Park, W. Optical Properties of Laterally Aligned Si Nanowires for Transparent Electronics Applications. *Nano Res.* 2011, 4, 817–823.

VOL.6 • NO.9 • 7879-7884 • 2012 A

- Ishikawa, F. N.; Chang, H.-K.; Ryu, K.; Chen, P.-C.; Badmaev, A.; Gomez De Arco, L.; Shen, G.; Zhou, C. Transparent Electronics Based on Transfer Printed Aligned Carbon Nanotubes on Rigid and Flexible Substrates. ACS Nano 2009, 3, 73–79.

- Yin, H.; Kim, S.; Kim, C. J.; Song, I.; Park, J.; Kim, S.; Park, Y. Fully Transparent Nonvolatile Memory Employing Amorphous Oxides as Charge Trap and Transistor's Channel Layer. Appl. Phys. Lett. 2008, 93, 172109.

- Uchida, T.; Kaneta, S.; Ichihara, M.; Ohtsuka, M.; Otomo, T.; Marx, D. R. Flexible Transparent Organic Light Emitting Devices on Plastic Films with Alkali Metal Doping as Electron Injection Layer. Jpn. J. Appl. Phys. 2005, 44, L282–L284.

- Yang, Y.; Jeong, S.; Hu, L.; Wu, H.; Lee, S. W.; Cui, Y. Transparent Lithium-Ion Batteries. *Proc. Natl. Acad. Sci. U.S.A.* 2011, *108*, 13013–13018.

- Milnes, A. G.; Feucht, D. L., Heterojunctions and Metal-Semiconductor Junctions; Academic Press: New York, 1972.

- Porti, M.; Avidano, M.; Nafria, M.; Aymerich, X.; Carreras, J.; Garrido, B. Conduction Mechanisms and Charge Storage in Si-Nanocrystals Metal-Oxide-Semiconductor Memory Devices Studied with Conducting Atomic Force Microscopy. J. Appl. Phys. 2005, 98, 056101.

- Chakraborty, G.; Chattopadhyay, S.; Sarkar, C. K.; Pramanik, C. Tunneling Current at the Interface of Silicon and Silicon Dioxide Partly Embedded with Silicon Nanocrystals in Metal Oxide Semiconductor Structures. J. Appl. Phys. 2007, 101, 024315.

- 41. Lee, C.; Wei, X.; Kysar, J. W.; Hone, J. Measurement of the Elastic Properties and Intrinsic Strength of Monolayer Graphene. *Science* **2008**, *321*, 385–388.

- 42. Huang, Y.; Wu, J.; Hwang, K. C. Thickness of Graphene and Single-Wall Carbon Nanotubes. *Phys. Rev. B* **2006**, *74*, 245413.

- 43. Zhang, D. B.; Akatyeva, E.; Dumitrică, T. Bending Ultrathin Graphene at the Margins of Continuum Mechanics. *Phys. Rev. Lett.* **2011**, *106*, 255503.

- Bao, W.; Miao, F.; Chen, Z.; Zhang, H.; Jang, W.; Dames, C.; Lau, C. N. Controlled Ripple Texturing of Suspended Graphene and Ultrathin Graphite Membranes. *Nat. Nanotechnol.* **2009**, *4*, 562–566.

- Yoon, D.; Son, Y.-W.; Cheong, H. Negative Thermal Expansion Coefficient of Graphene Measured by Raman Spectroscopy. *Nano Lett.* **2011**, *11*, 3227–3231.

- Mounet, N.; Marzari, N. First-Principles Determination of the Structural, Vibrational and Thermodynamic Properties of Diamond, Graphite, and Derivatives. *Phys. Rev. B* 2005, *71*, 205214.

- 47. The electrical measurements were taken on a GCTM device with channel dimensions (*W*/*L*  $\approx$  4.5  $\mu$ m/30  $\mu$ m) and Ti/Al (10 nm/100 nm) source/drain contacts due to the difficulties in probing the monolayer graphene electrodes.

- Bae, S.; Kim, H.; Lee, Y.; Xu, X.; Park, J.-S.; Zheng, Y.; Balakrishnan, J.; Lei, T.; Ri Kim, H.; Song, Y. I.; *et al.* Rollto-Roll Production of 30-Inch Graphene Films for Transparent Electrodes. *Nat. Nanotechnol.* **2010**, *5*, 574–578.

- Shimizu, T.; Haruyama, J.; Marcano, D. C.; Kosinkin, D. V.; Tour, J. M.; Hirose, K.; Suenaga, K. Large Intrinsic Energy Bandgaps in Annealed Nanotube-Derived Graphene Nanoribbons. *Nat. Nanotechnol.* **2011**, *6*, 45–50.

- Zhang, Y.; Tang, T.-T.; Girit, C.; Hao, Z.; Martin, M. C.; Zettl, A.; Crommie, M. F.; Shen, Y. R.; Wang, F. Direct Observation of a Widely Tunable Bandgap in Bilayer Graphene. *Nature* 2009, 459, 820–823.

- Lui, C. H.; Li, Z.; Mak, K. F.; Cappelluti, E.; Heinz, T. F. Observation of an Electrically Tunable Band Gap in Trilayer Graphene. *Nat. Phys.* 2011, 7, 944–947.

- 52. Geim, A. K. Graphene: Status and Prospects. *Science* **2009**, *324*, 1530–1534.

- Castro Neto, A. H.; Guinea, F.; Peres, N. M. R.; Novoselov, K. S.; Geim, A. K. The Electronic Properties of Graphene. *Rev. Mod. Phys.* 2009, *81*, 109–162.

- 54. ITRS 2010: Report Memory Assessment 2010. http://www. itrs.net.

KIM ET AL.